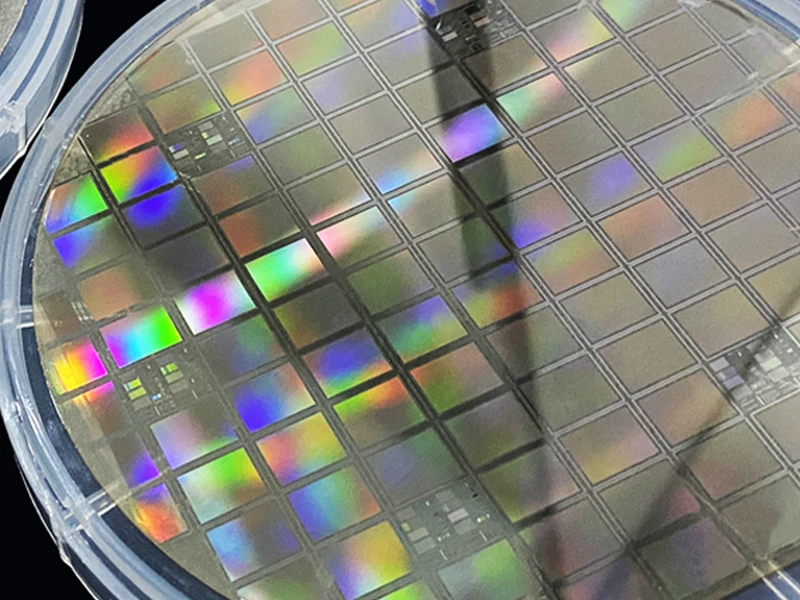

Among the hundreds of processes in chip manufacturing, one technique remains inconspicuous yet critically important: wafer electroplating.

I. Why Electroplating Is Indispensable

In the nanoscale chip era, aluminum (Al) interconnects can no longer meet extreme demands for speed, power consumption, and integration density.

Copper (Cu), with its lower resistivity and stronger electromigration resistance, has replaced aluminum as the mainstream interconnect material.

However, a major challenge emerged: copper cannot be precisely patterned by conventional etching due to the lack of suitable volatile byproducts.

The semiconductor industry pioneered the Damascene Process, in which electroplating serves as the core step.

In brief, the Damascene Process involves:

- Etching trenches and vias into an insulating layer such as SiO₂.

- Filling these trenches and vias with copper via wafer electroplating.

- Removing excess copper using chemical mechanical polishing (CMP) to planarize the surface, leaving patterned copper interconnects.

II. Core Flow and Technical Highlights of Electroplating

Wafer electroplating is far from ordinary plating; it is an ultra-precise electrochemical process.

1. Pre-Treatment: Barrier Layer and Seed Layer Deposition

- Barrier LayerA thin barrier layer (typically Ta, TaN, or similar materials) is deposited first to prevent copper diffusion into silicon and dielectric materials, which would cause device contamination and failure.

- Seed LayerA thin copper film (tens to 100 nanometers) is deposited onto the barrier layer via PVD.This conductive copper layer acts as the cathode for electroplating, providing a uniform current path.The continuity and uniformity of the seed layer are critical for high-quality plating.

2. Electroplating Process: The Chemistry of Superfilling

- The seeded wafer is immersed in an electrolytic bath containing copper ions and specialized additives, serving as the cathode.

- When current is applied, copper ions gain electrons at the wafer surface and deposit as metallic copper.

The key technology lies in three synergistic additives:

- Suppressor: A large polymer such as PEG that forms a surface film to slow deposition across the wafer.

- Accelerator: A small sulfur-containing molecule such as SPS that diffuses to trench bottoms, locally accelerating copper growth.

- Leveler: A macromolecule that adsorbs preferentially at trench openings to suppress over-deposition.

Together, they enable bottom-up superfilling, where copper grows faster at the bottom of features than at the top, enabling void-free filling of high-aspect-ratio structures.

3. Post-Treatment: Annealing and CMP

- AnnealingElectroplated copper has a fine-grained, loose structure.High-temperature annealing promotes recrystallization, enlarges grain size, reduces resistivity, and improves stability.

- Chemical Mechanical Polishing (CMP)Excess surface copper and the underlying barrier layer are removed via precision polishing and planarization, leaving a smooth, flat surface ready for the next interconnect layer.